Operating Systems: Three Easy Pieces Ch. 36

Input/output device (I/O)

- System Architecture

- Hierarchiacal structure

- CPU, memory, memory BUS

- I/O bus

- PCI

- Peripheral Component Interconnect

- High-speed I/O devices such as graphics

- Peripheral bus

- Lower speed bus

- SATA, USB

- connects to disks, mice, keyboards

- PCI

- Reasons

- Physics, cost

- a high-performance memory bus does not have much room to plug devices and such into it

- Modern Computer system

- DMI

- Direct Media Interface

- Devices connect to the chip

- ATA → The AT Attachment

- SATA, eSATA

- USB

- Universal Serial Bus → Keyborads, Mice

- PCIe

- Peripheral Component Interconnect Express

- Higher performance → networ, NVMe(High speed)

- DMI

- Canonical Device

- Hardware interface

- present interface that allows the system software to control its operation

- All device have specified interface and protocol

- Internal structure

- specific and responsible for implementin the abstraction the devide presents to the system

- Simple device such as CPU, memroy, RAID controller

- thousands of line of firmware

- specific and responsible for implementin the abstraction the devide presents to the system

- Hardware interface

- Canonical Protocol

- Status register → current status

- Command register → to perform certain task

- Data register → pass data to device

- Four steps

- Pooling, waiting for the device is ready to receive a command

- Sending data

- Programmed I/O

- Command using command register

- OS waits for device poerform the task

- Lowering CPU overhead

- interrupt

- Instead of pooling

- Interrupt Service Routine

- Interrupt Handler

- Allows overlap of computation and I/O

- using interrupts is not always the best solution

- Interrupt is expensive, inefficient in the case of simple I/O interrupt

- Hybrid, two-phased approach

- First Poll

- After certain time, interrupt

- if a device is fast, it may be best to poll; if it is slow, interrupt

- coalescing

- device need to raise an interrupt first waits for a bit

- multiple interrupts can be coalesced into a single interrupt delivery

- Interrupt is expensive, inefficient in the case of simple I/O interrupt

- interrupt

- More Efficient Data Movement With DMA

- when using programmed I/O (PIO) to transfer a large chunk of data to a device, the CPU is once again over burdened with a rather trivial task

- Copying the data using CPU → trivial task

- Direct Memory Access (DMA)

- OS program DMA engine by telling it where the data lives in memory, how much data to copy, and which device to send it to.

- DMA is complete → raise the interrupt, and the OS knows the transfer control is completed

- when using programmed I/O (PIO) to transfer a large chunk of data to a device, the CPU is once again over burdened with a rather trivial task

- Methods Of Device Interaction

- explicit I/O instructions

- previleged instructions

- OS controls device, directly communicate with the device

- Memory mapped I/O

- the hardware makes device registers available as if they were memory locations

- OS issues a load (to read) or store (to write) the address

- The memory-mapped approach is nice in that no new instructions are needed to support it

- explicit I/O instructions

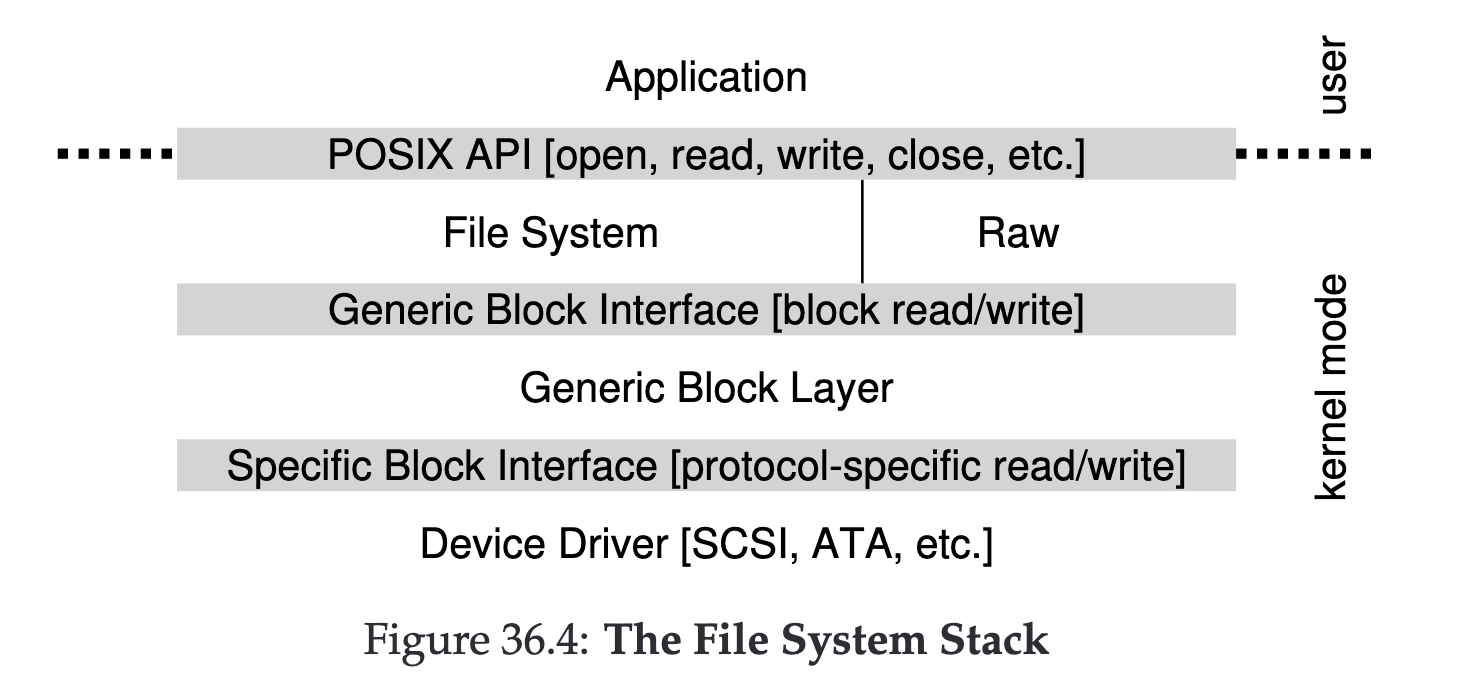

- Device Driver

- how to fit devices, each of which have very specific interfaces

- OS must know in detail how a device work

- Device Driver solve the question

- 70% of OS code is found in device drivers

- Window is high as well

- An IDE disk presents a simple interface to the system, consisting of four types of register: control, command block, status, and error

- Basic Protocol

- Wait for ready

- Write parameter to command register

- Start I/O

- Data transfer

- Handle interrupts

- Error Handling

- Basic Protocol

- Who started first?

- Not clear

- people built these early machines, it became obvious that I/O support was needed.

- Hierarchiacal structure